AT50で使うつもりのBias-Tの設計の続き。こないだ一応設計したつもりだったけど、インピーダンスのマッチングが取れてない状態じゃダメだと気づいたので、そのへんの条件を変えてシミュレーションしてみる。

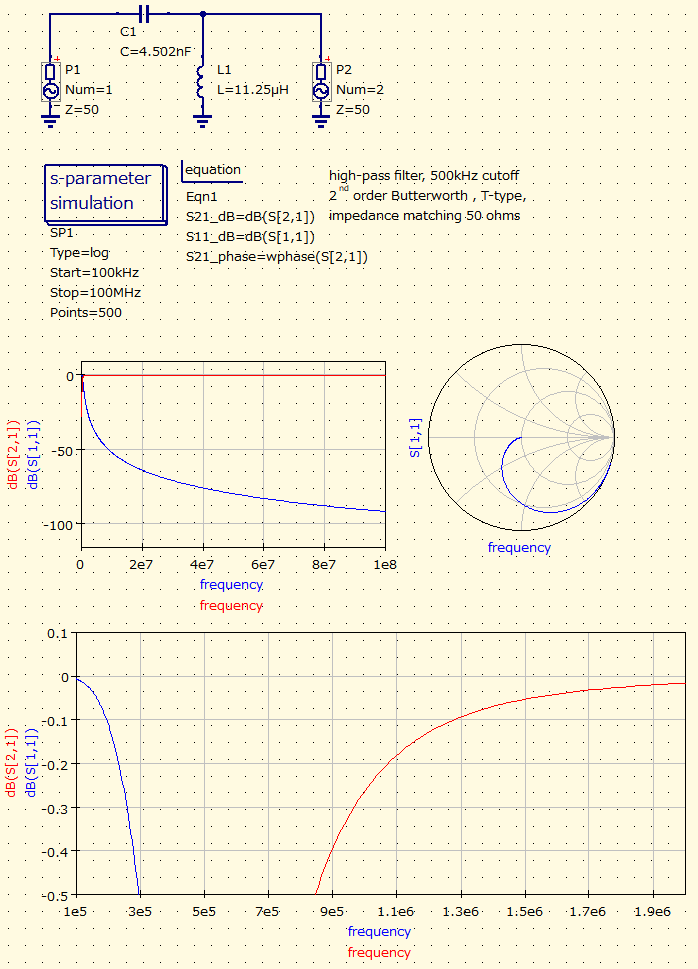

基本形(50Ω)

まずは、基本として入出力インピーダンスを50Ωとした場合。前回の設計と同じ(カットオフ周波数は500kHz)だけど、シミュレーションの上限周波数を100MHzまで広げてみた。

インピーダンスを上げる

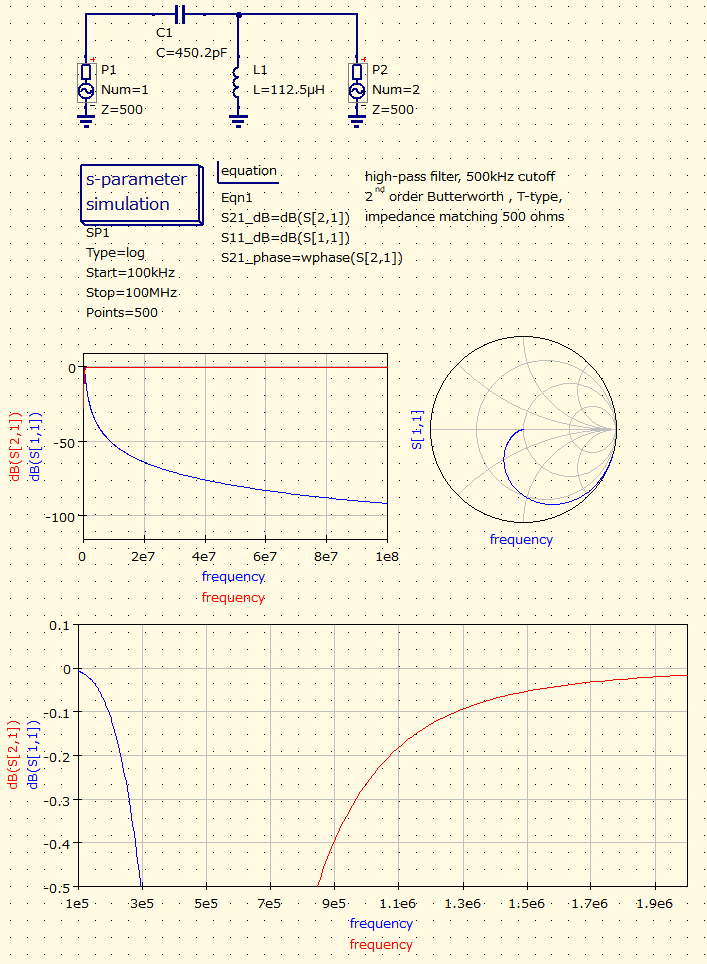

500Ω

10倍の500Ωの場合。

単純にCが1/10、Lが10倍になるのね。グラフは変らない(当たり前)。

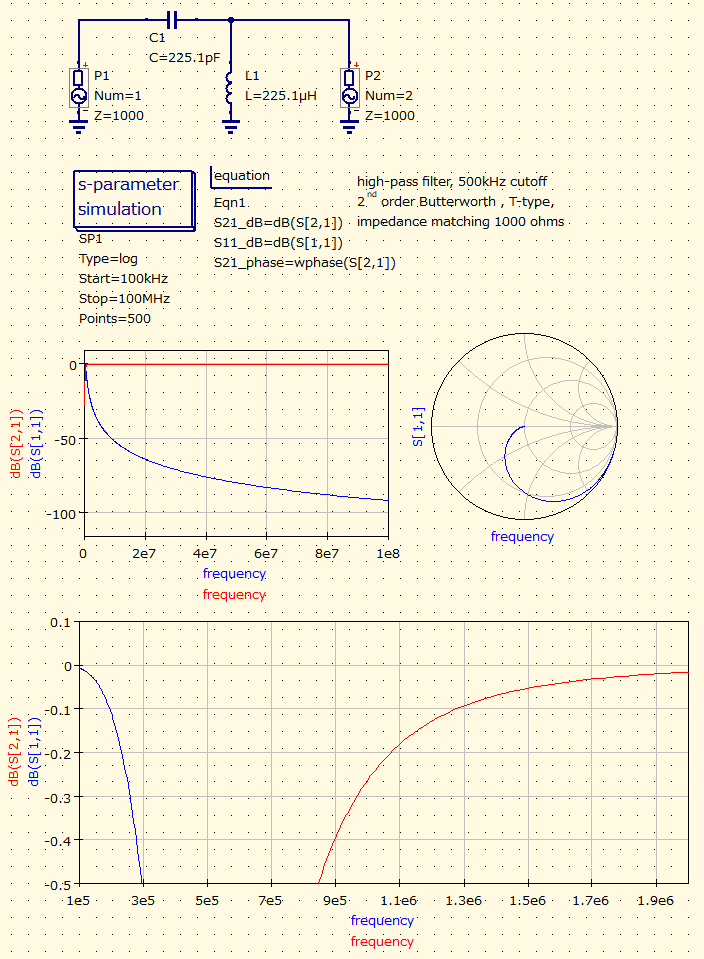

1kΩ

Cが1/20、Lが20倍。

インピーダンスを下げる

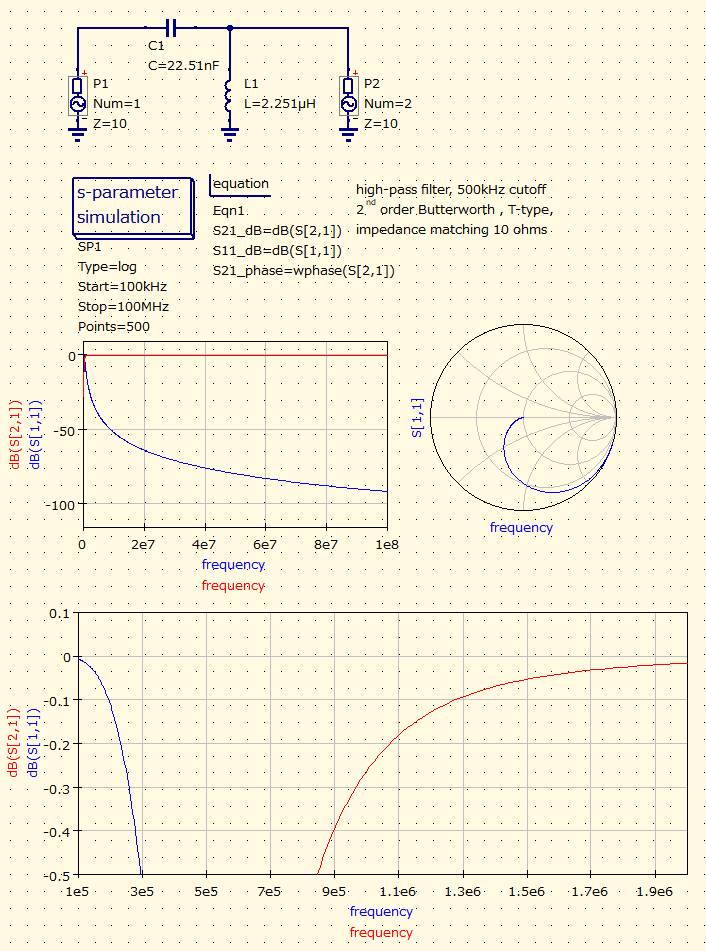

10Ω

インピーダンスが1/5。Cが1/5、Lが5倍。

ということで、これ以上はやるまでもないので省略。

設計案

以上の結果を見て、再設計。入出力インピーダンスを50Ωとして、CとLを変えたものでシミュレートしてみる。

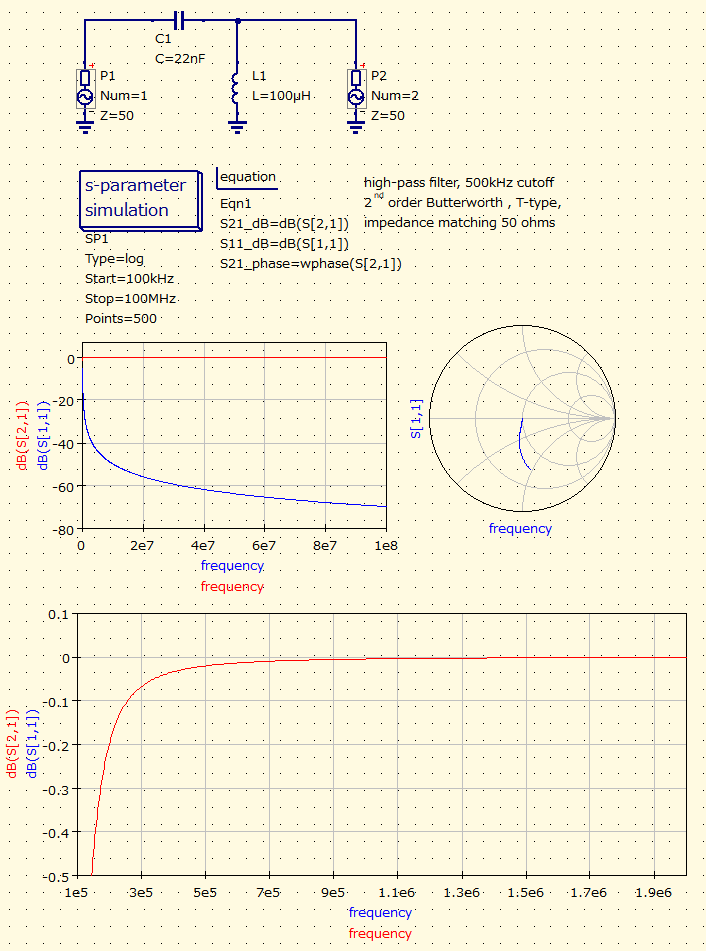

C: 22nF、L: 100μH

1.8MHzはまったく問題なく通る。というか、カットオフ周波数が非常に下がった格好になる(当たり前)。

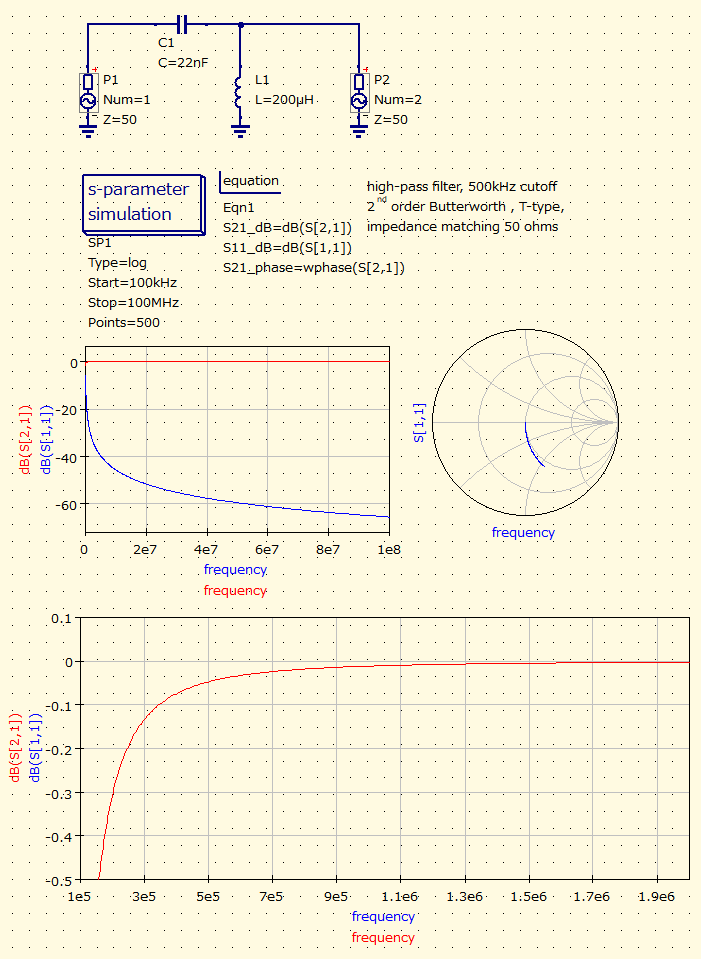

C: 22nF、L: 200μH

Lを大きくすると下の方(例えば3MHzとか)の減衰が少しだけ大きくなる。まぁ、誤差の範囲みたいなものだけど。

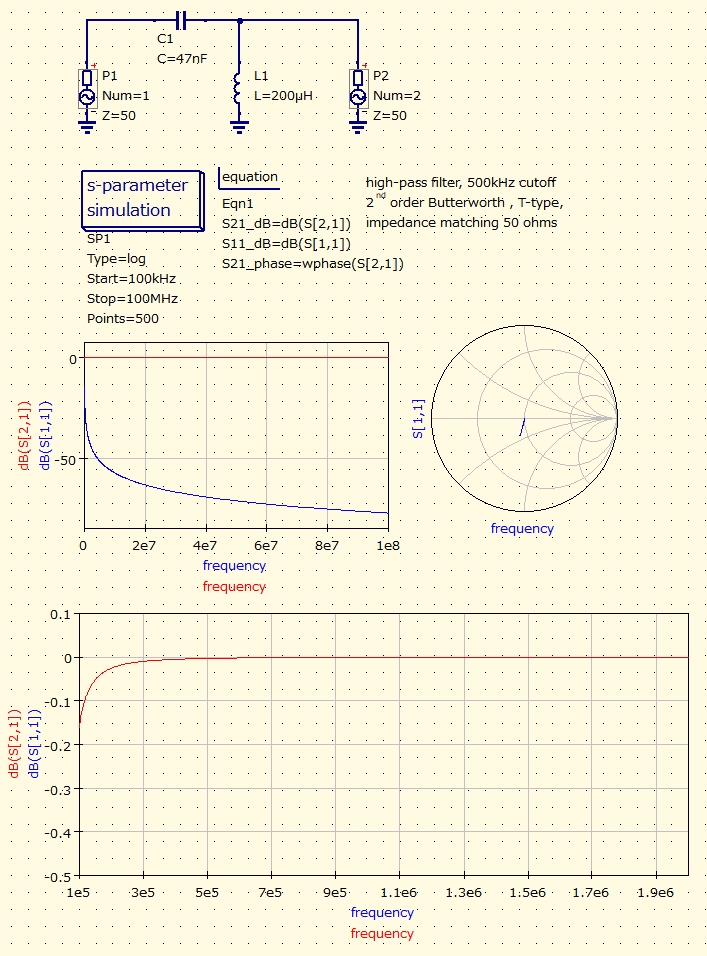

C: 47nF、L: 200μH

Cを大きくすれば予想通り下の方は改善する。47nF(0.047μF)にもなると、もうほとんどDCを分離するだけみたいになった。

C: 10nF、L: 100μH

上を踏まえて、このあたりが現実的かなと思う値で。

1.8MHzあたりが少し減衰。まぁ、0.03dB位なので気にするほどではない。が、Bias-Tは入口と出口で使うので、減衰量は二倍になることには注意。Cはもうちょっと大きめにしておくか。

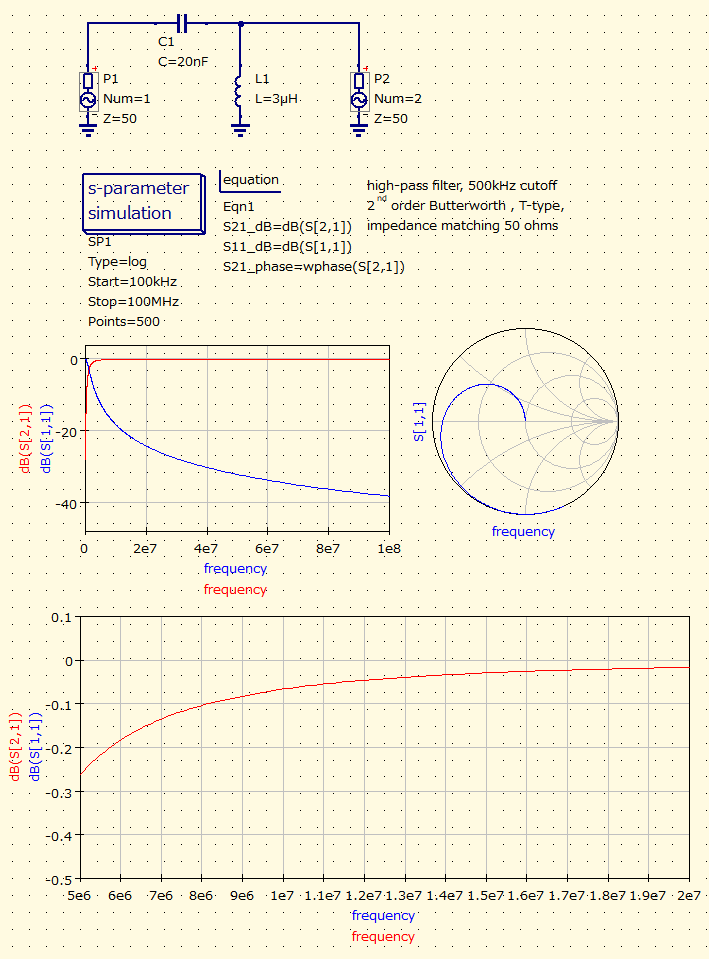

C: 20nF、L: 2μH

ということで、Cを20nFにした場合。なお、Lは2μFで。Lは周波数が上がるとインダクタンスが大きく減少することがわかっているので、周波数が高くなった場合をチェックしておく。こないだの実測で、T50-43に5回巻きの場合、1MHz付近で11μH、15MHz付近で3μH強。ということで、小さめの2μHで試してみる。

15MHz付近で-0.03dB位。10MHz付近では-0.07dB位だけど、このあたりだとLのインダクタンスはもっと大きいのでこんなには減衰しないだろう。

T50-43に16回巻けば計算上は100μHを超えることになる。それでインダクタンスを測定してみて良さげならBias-Tとして実際に組んでみる。

コメント