HT82V739のポップノイズを\(\overline{CE}\)で消せなかったという記事を書いたところ、Twitterで色々とコメントを貰った。その中に、\(\overline{CE}\)をトリガにしてVREFなどをオシロで見てみたらというアイデアがあった。少々時間が経ったが、やってみた。

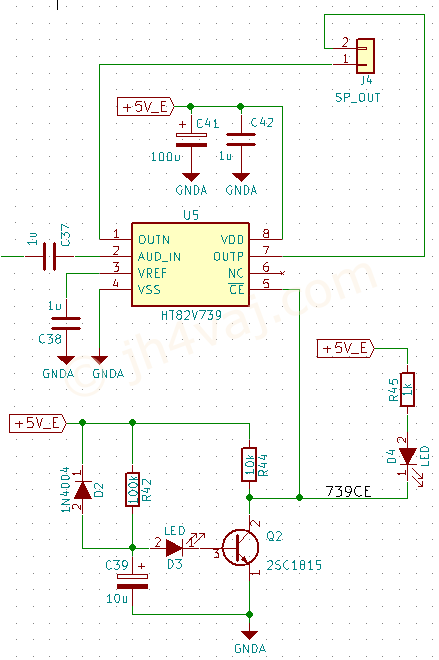

回路図を再掲。

入力信号はなし(C37を通じてGNDに接続)とする。

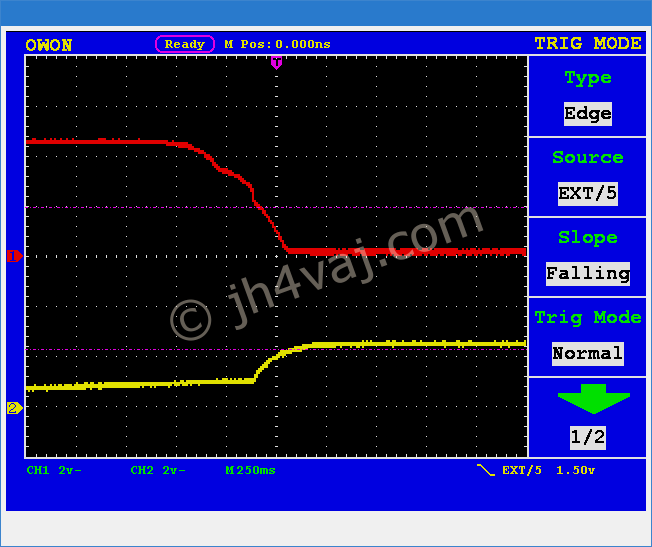

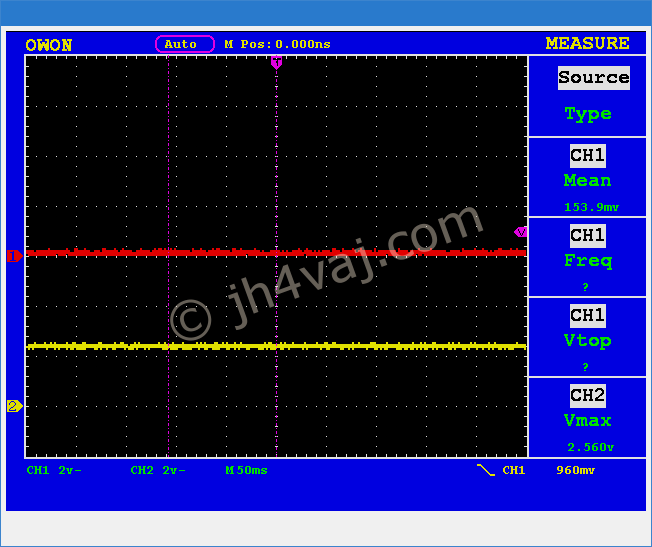

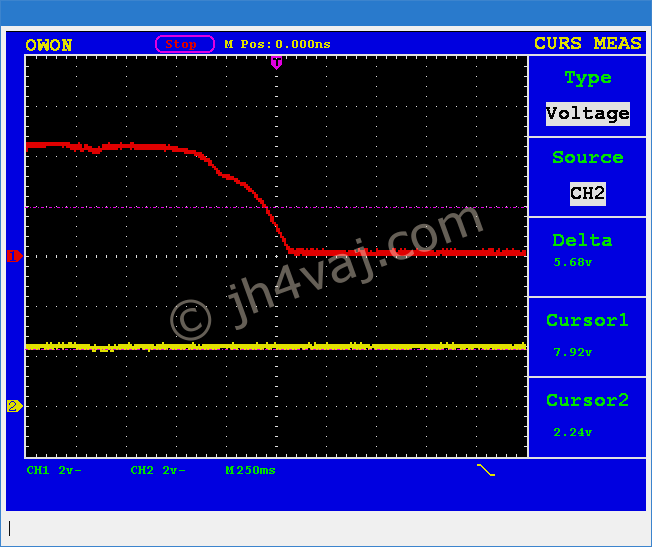

まずは、通常の動作状態。Ch1: \(\overline{CE}\)、Ch2: VREF。

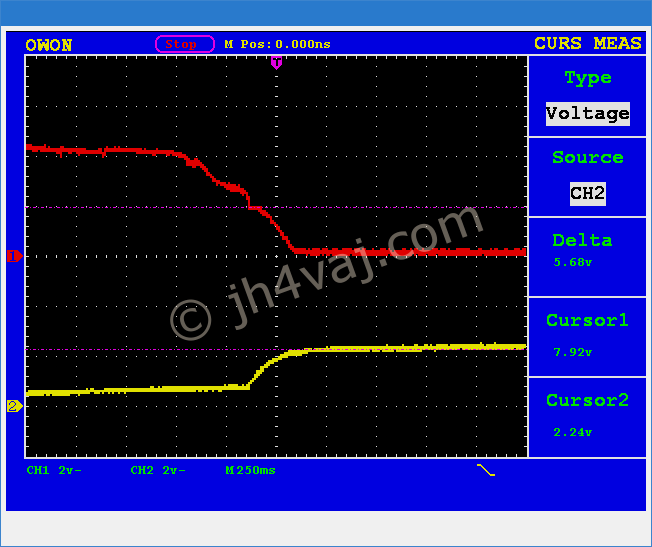

測定信号は同じで、電源投入時。

\(\overline{CE}\)がイネーブルになってからVREFが立ち上がるらしい。スタンバイ状態はほとんど電力を食わないことが特長になっているので、VREFもカットされているということか。

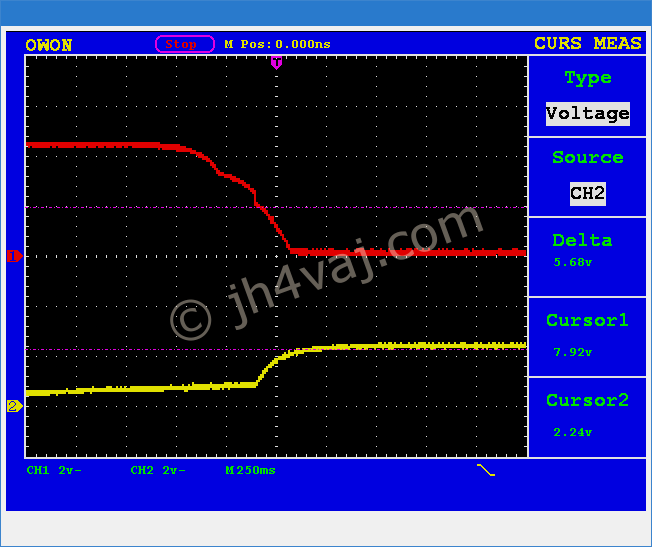

続いては、Ch2: 入力(ピン2)の様子。

VREFと同じ挙動。

今度は、外部で強制的に1/2VDDを作って(10kΩ二つで分圧)、それをVREFに入れてみた。こんなことをやっていいのかどうかわからないけど、まぁ、実験ということで。Ch2: VREF。

当たり前だけど、VREFは最初から約2.5V。

このときの入力ピンも見てみたら、こっちも2.5Vで一定になっていた。

つまり、VREFと同じレベルになっている。

念のため、VREFと入力の間を100kΩでつないでみた。

波形上は変らない。

いずれの場合でも、ポップ音は発生する。HT82V739はそういう石なんだろう。残念だけどしょうがない。

続き

HT82V739のポップノイズ、その三

前回の話はこちら。この記事に対してコメントを頂戴した。差動信号を見るのには、Ch1とCh2で測定して差分を出せばよいというのは、まったくその通りで、一応、考えはしたのだけど、外部トリガを使おうにもプローブが二本しかないので諦めていた。でも、...

コメント

二つ疑問があります。

・出力側でポップ音そのものの波形を観測しましたか。

・/ce信号の変化が非常に緩やかなのは想定外でした。

ロジック入力に変化の緩慢な信号を入力するとスレッショルドレベル附近の

ノイズに応答して動作がばたつく可能性があるでせう。尤も入力端子がシュ

ミット入力になつてゐればこれはありませんが。この品種はどうですか。

さういへば、最初の回路で/ce信号の発生はどうしてゐましたか。

高速信号での切り替へでしたか。それならばこの推測も外れです。

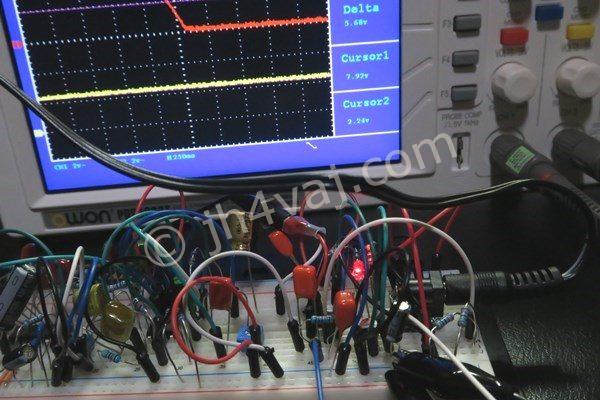

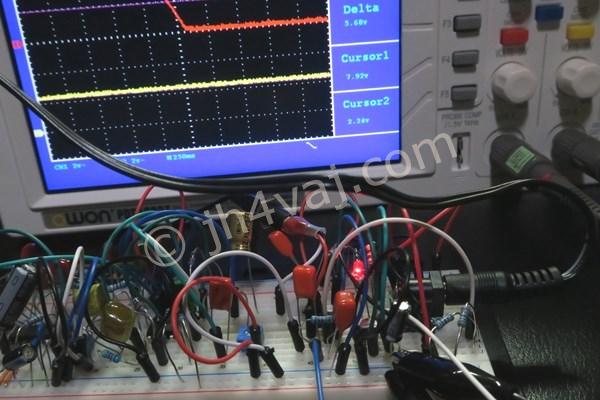

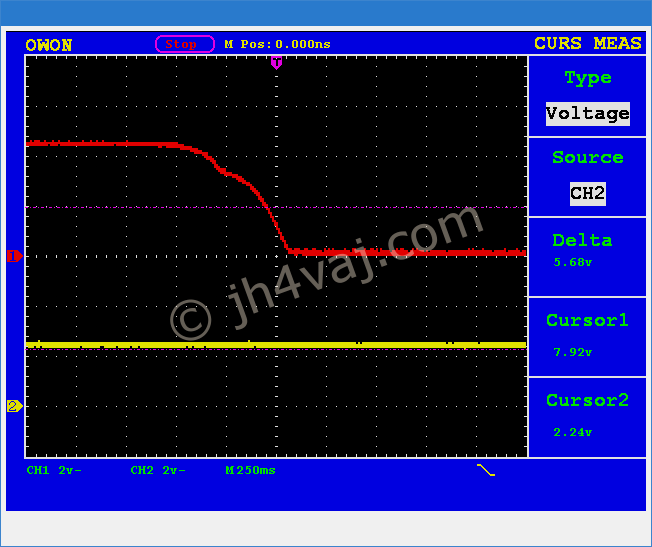

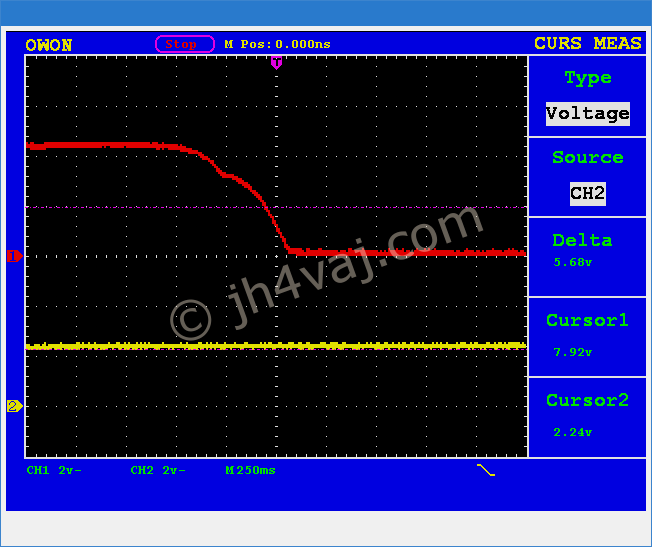

出力はGNDと共通ではないため測定していませんでした。ですが、試しに測定してみました。Ch1が\(\overline{CE}\)、Ch2がピン7のOUTPとGND間です。

それから、\(\overline{CE}\)はメカニカルSWを想定して、ブレッドボードにジャンパピンを挿す方法でもやってみていました(10kΩでプルアップしておき、ジャンパ線を手動でGNDに接続)。これでもポップ音が出ることは確認しています。若干、小さくなる傾向ですが、消えることはありません。ついでなので、このときの様子も測定してみました。

\(\overline{CE}\)がシュミット入力という記述はなさそうですが、この方法でもポップ音を消すことはできないので諦めたという状況です。

動作開始時、差動出力の片側に電圧不連続が見えますね。

但同相信号なら打ち消されて殆どなくなる訣です。

GNDから浮いた差動出力を観測するにはオシロスコープのch1、ch2

で各差動出力を観測して差分を計算させ、トリガ端子の入力をトリ

ガとします。

イネーブルにする場合はショートピンを挿すときですね。挿すとき

は抜くときよりも接触が断続しさうです。

それに音が小さくなる傾向があるのでせう。

/ce端子をプルダウンしてショートピンをホット側に設置して実験す

るのはどうでせう。これならピンを抜くときに動作開始となりますか

ら。

続きを別記事にしました。

https://www.jh4vaj.com/archives/5560